音频 DAC 典型设计:

USB Interface

USB 音频界面(USB audio interface)通常使用 UAC/UAD 协议实现与主机的音频数据传输。设备通常使用 MCU、FPGA 或专用芯片处理协议转换。从用户功能来说,主要包括麦克风、声卡和其它音频设备的功能控制和接口标准,但其内部可以有多种复杂的功能。

以 Comtrue Inc. 生产的 CT7601 系列音频芯片为例,其将 USB 2.0/1.1 接口异步转换为多路 I2S 或 DSD 以及 SPDIF 协议。并且允许使用定制固件通过内置 8051 控制其它芯片。此类芯片通常只需使用软件写入固件即可使用,但固件开发工具往往不对个人开放。CT7601 也是如此,所以不逆向开发的前提下,可以收集不同成品的固件进行修改。工具及公开固件

在 PCB 设计上,注意:

- USB 差分 90 ohm 阻抗

- 芯片 IO 供电就近使用去耦电容,芯片下使用完整供电平面,供电层边缘向内收缩。参考手册: 电源静噪和去耦

- I2S 输出串联 22/33 ohm 匹配阻抗,光纤 SPDIF 需串联 100nF 电容。I2S 须注意 MCLK 以及 SCLK 产生的串扰。

- 离板信号使用合适的磁珠以及电容进行滤波,并将磁珠作为铺铜分界线。

使用村田 SimSurfing 工具可快速选型设计滤波器。

Audio Codec

音频芯片之间通常使用 I2S 协议(假设包含 Left-Justified 等协议)进行沟通,可认为其包含四条数据线:

- MCLK 主时钟:为模数芯片提供用于转换、信号处理或调制等功能以及内部基于 Delta-Sigma 的需求,通常不使用或使用单独的时钟。

- SCK 同步时钟:用于同步 I2S 数据传输。从模式时由主机提供,主模式时由内部自己产生。需注意数据可同步于上升沿或下降沿。

- SD 串行数据:以二进制补码的形式在数据线上传输。在 LRCLK 变化后的第一个或第二个 SCK 脉冲,先传输最高位(MSB)。

- LRCLK 声道同步:既可以在 SCK 的上升沿,也可以在 SCK 的下降沿变化。既可以高电平表示左声道也可以低电平表示。从设备在 SCK 的上升沿采样 LRCLK 信号。

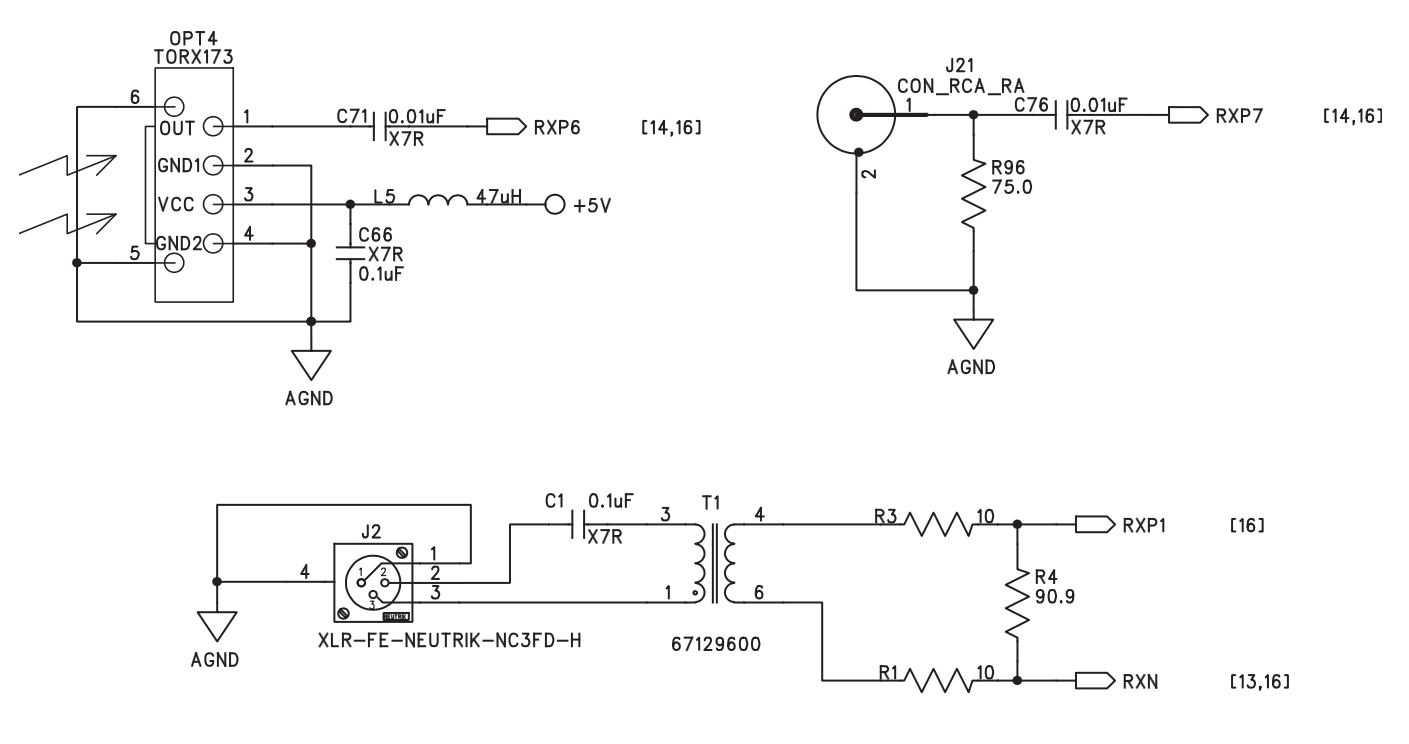

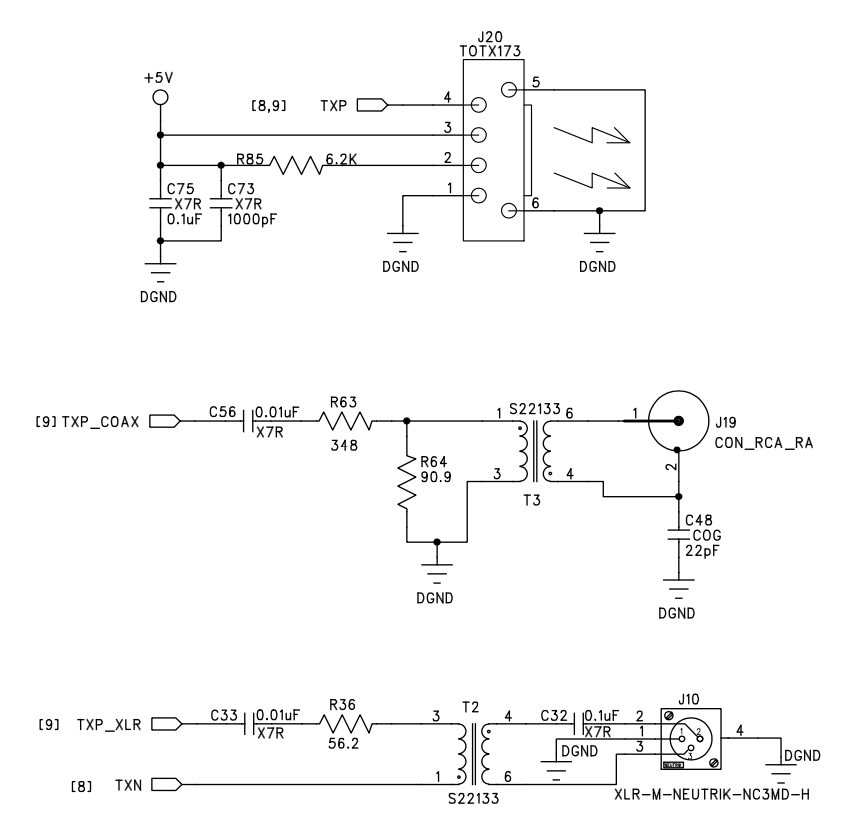

在设备间长距离传输数字信号时,SPDIF(AES/EBU 等相关标准)是更好的选择,采用了双相相位编码(BMC),将时钟信号和数据信号混合在一起,只需单根信号线即可传输,方便通过使用同轴线、差分屏蔽线或光纤进行远距离传输。参考 Cirrus Logic 的 CDB8416 设计:

D/A Converter

音频 DAC 将数字编码通过调制器(通常为 Sigma-Delta 架构)生成电压或电流模拟信号,通过运放进行电平转换、高通低通滤波、功率放大等操作,最后输出到从设备。以 ES9018K2M 为例,其支持 I2S、DSD 以及 SPDIF 输入,可复用 IO 自动检测输入协议:

DAC 在数字信号输入后进行数字滤波,其中主要有两种滤波器:

Oversampling Filter

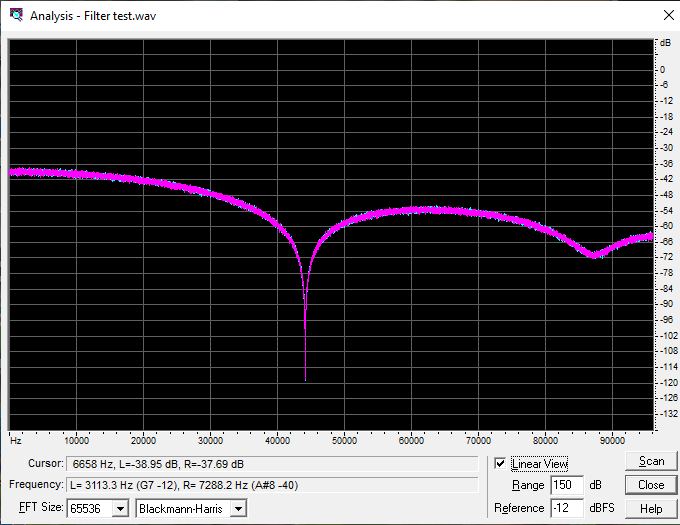

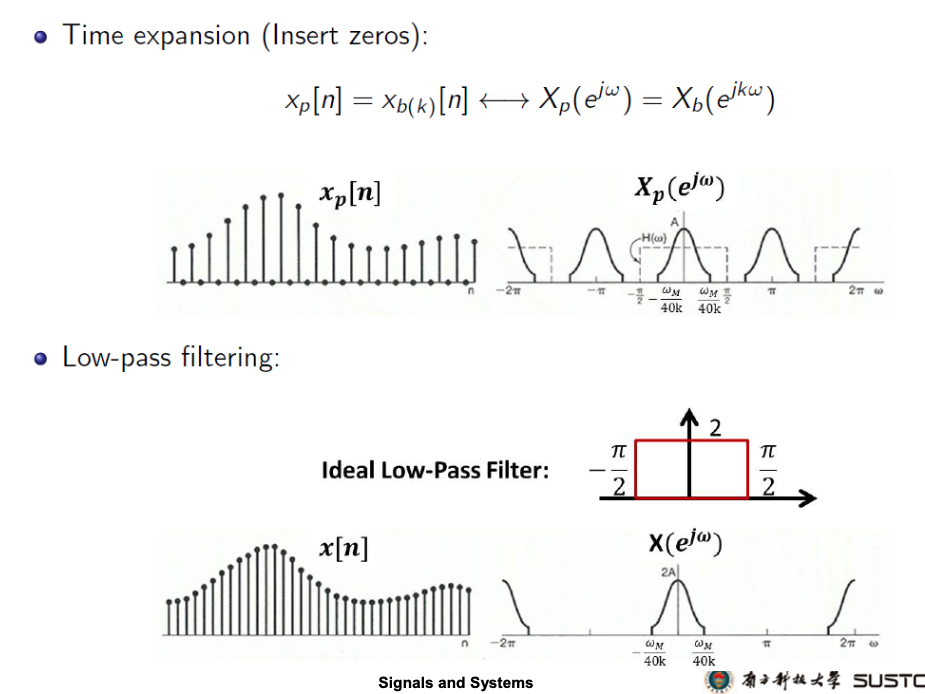

超采样滤波或 PCM 滤波。通常存储采样频率为有效频率两倍,对于直接将离散数字信号转换为阶跃模拟信号的理想 DAC ,在频谱上将会产生一簇簇边带。可从 Stephen Dawson 的测试图中看出:

「而我们所需要的仅仅是中心频率为 0 的那半个边带,其他的全是噪声,这就是为什么在 D/A 后面一定要跟一个低通滤波器的原因,该滤波器也叫做 "抗混叠滤波器" (anti-aliasing filter)。由于谱线簇相邻很近,需要过渡特性十分陡峭。这样的滤波器特性在实用工程上根本无法做到。」来源:大繁至简

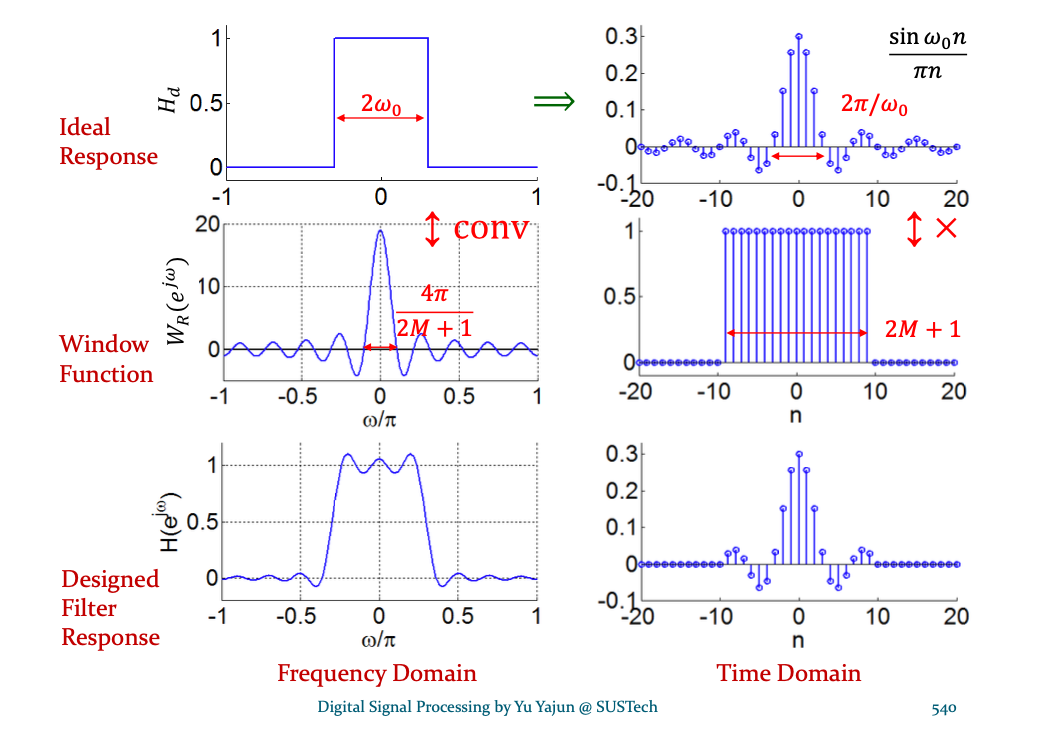

而通过差值后,就方便于设计接近完美的数字滤波器,来增加谱线簇之间的距离,有利于模拟滤波器的设计。设计数字滤波,首先将理想频域响应转换成时域响应,会发现时间范围无限。对于数字信号处理,需要限定计算的时间范围(加窗)。

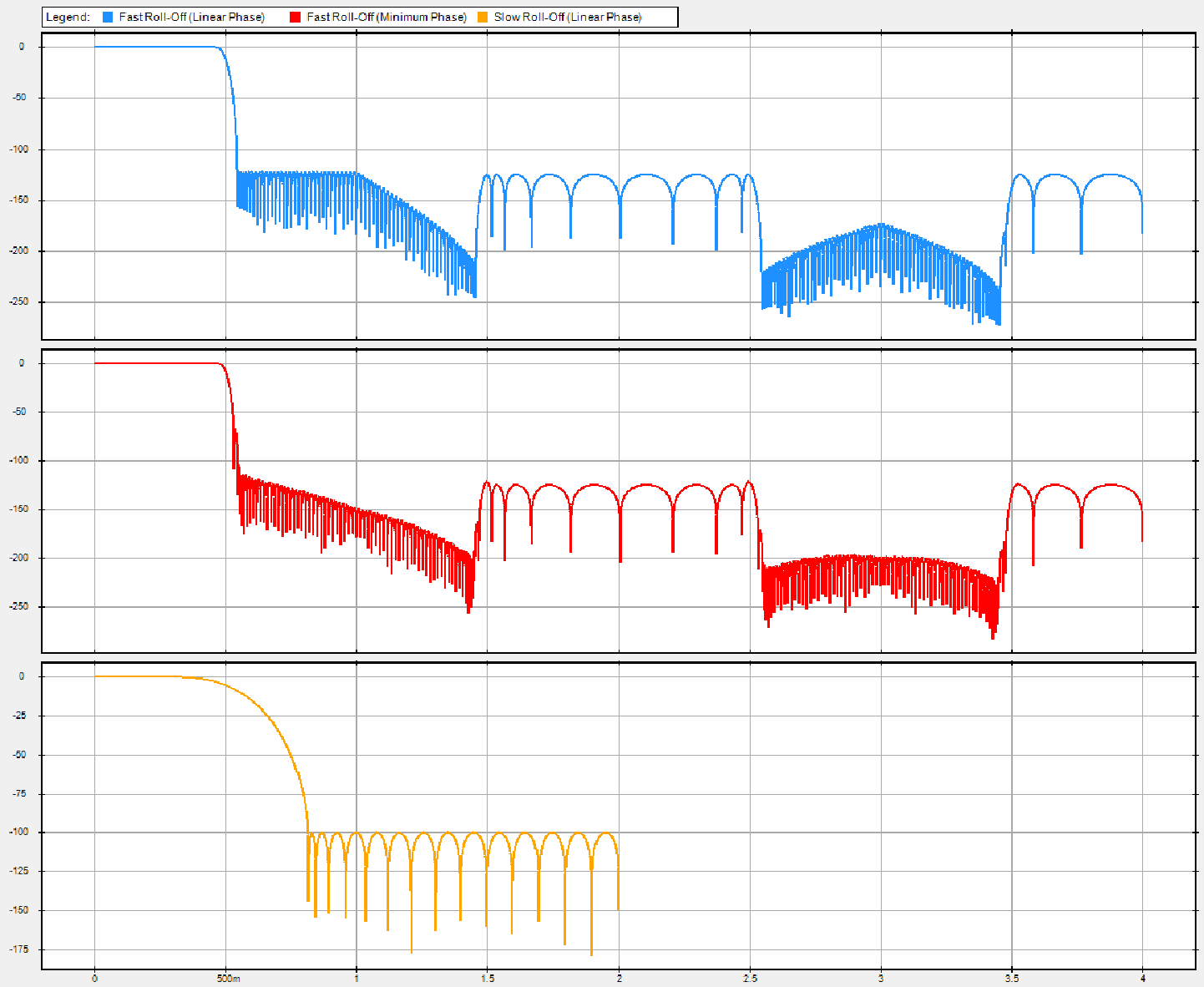

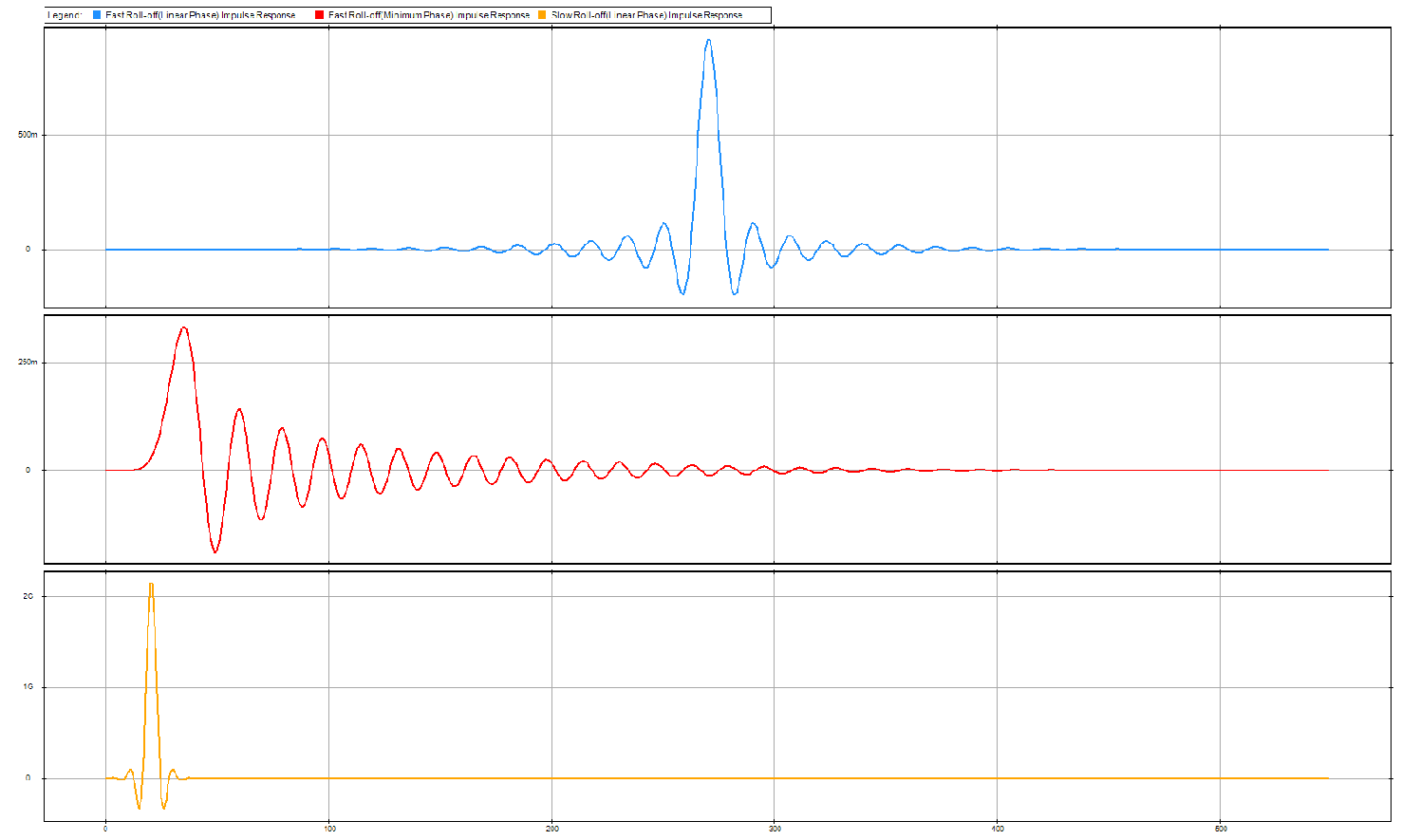

改变加窗函数可调整滤波器的性质,常见有 Rectangle、Hanning、Hamming 等。而音频处理常用 Roll-off 的斜率、时间的延迟、相位的变化等性质来命名,以 ES9018K2M 为例:

在 Stephen Dawson 的文章中可以看到实际测试的脉冲响应,并且滤波不可避免的将产生振铃(Ringing)和过冲(Overshoot),在 1kHz 的方波下可以明显观察到,并且过冲量不随方波频率变化而改变。通常越陡峭的滤波器越为明显。虽然在模拟滤波器中也会出现类似情况,但数字滤波不会有潜在的自激风险,可以更自由地按需求选择。而对于音乐回放,人耳几乎无法分辨区别。

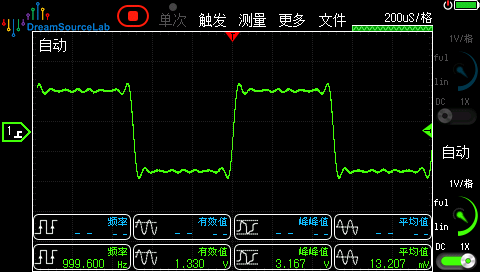

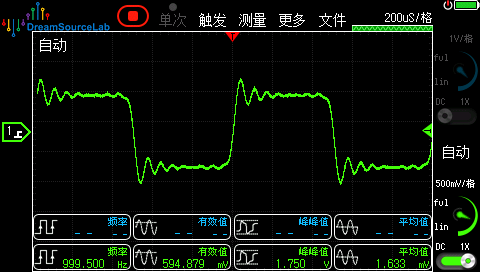

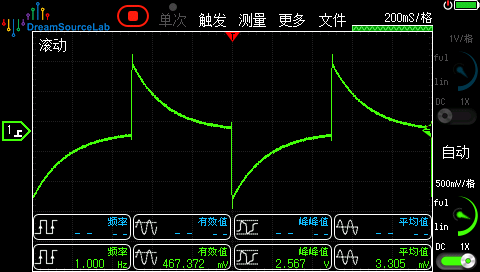

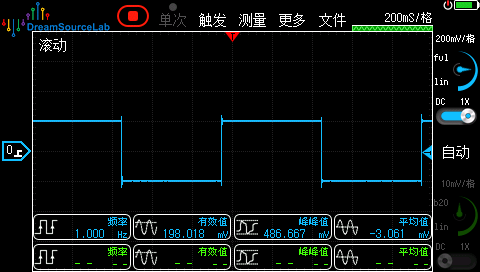

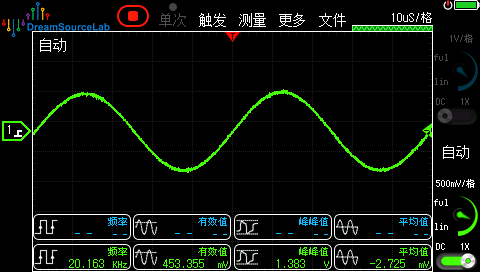

测量不同设备输出 1kHz 方波(按顺序为 B360i 板载、iPad Air、Desk Cube):

De-emphasis Filter

数字去加重滤波器,是模拟录音时代的产物。由于高频信号通常振幅较小,为了提高 SNR 可以将高频信号放大后传输。数字时代也有降低高频小振幅信号量化失真的作用。

Current or Voltage Output

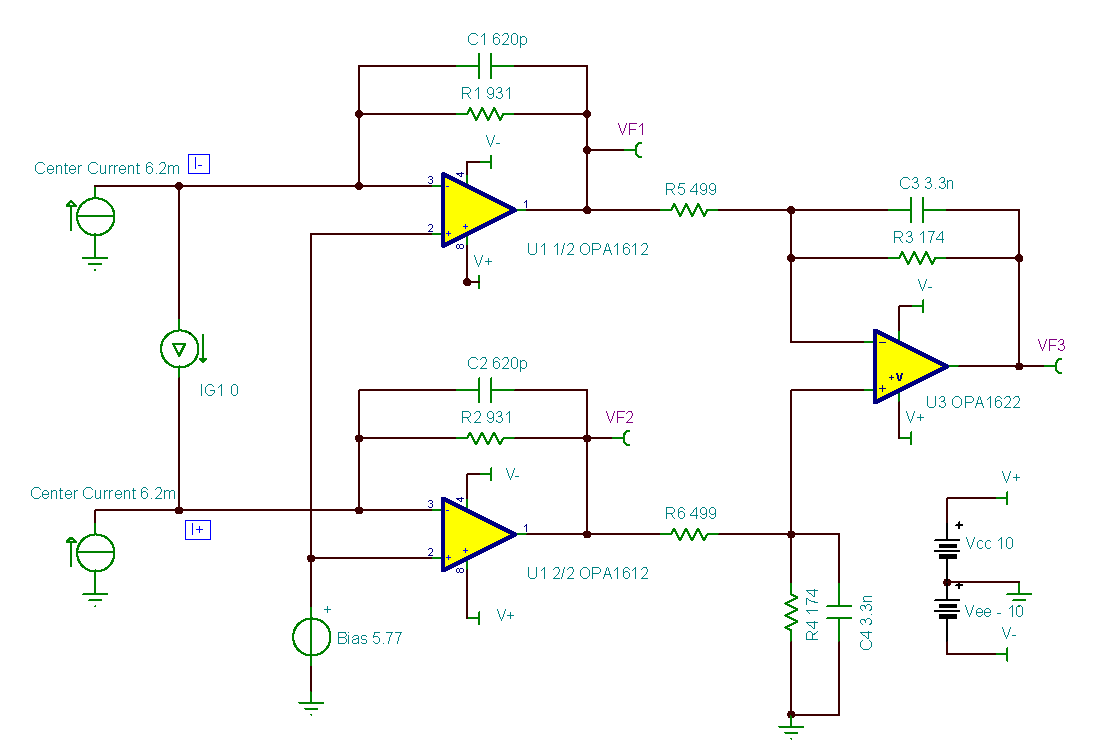

许多高性能 DAC 都支持采用电流或者电压输出模式,并且电流输出通常具有稍高的动态范围以及失真表现。通常情况下,两者都可看作具有固定内阻的电压源或并联了固定电阻的电流源,并且通常具有偏置电压/电流。如采用电流输出,可使用一级运放组成 I/V 电路转换为电压输出,根据 Ti 的参考设计:

在交流信号下,放大倍数为 $V_{OUT}/V_{DAC}=2320/806$ 。而直流输出电压为 $V_{OUT}=V_{BIAS}\left(1+2320/806\right)$ 。当需要直流输出电压为 0 V 时,可反求出所需偏置电压。偏置电压常使用 DAC 模拟输出供电进行电阻分压。

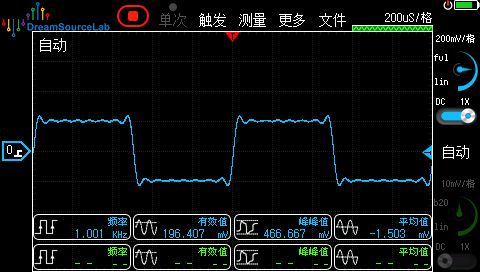

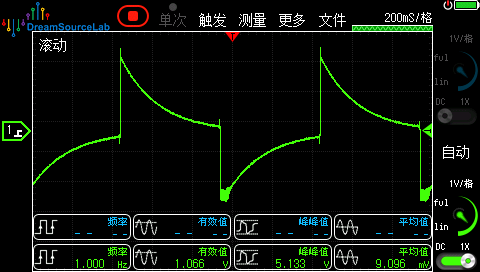

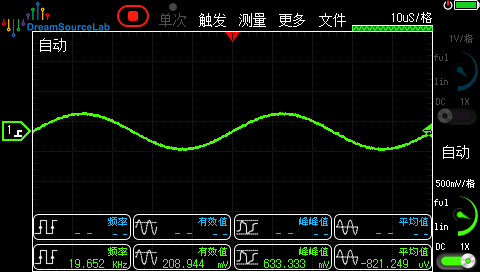

对于电压输出,由于偏置电压的存在,往往需要 RC 高通滤波器。为了避免小体积电容的非线性、高阻值电阻的高噪声、以及较好的低频响应,通常需使用体积较大的 uF 级别薄膜或电解电容。如保留偏置电压,则在放大电路中需要更高的电压供电。两者皆有优缺点,但我认为电流输出的性能更好并且可以输出直流信号,值得一试。1Hz 的方波测试(按顺序为 B360i 板载、iPad Air、Desk Cube):

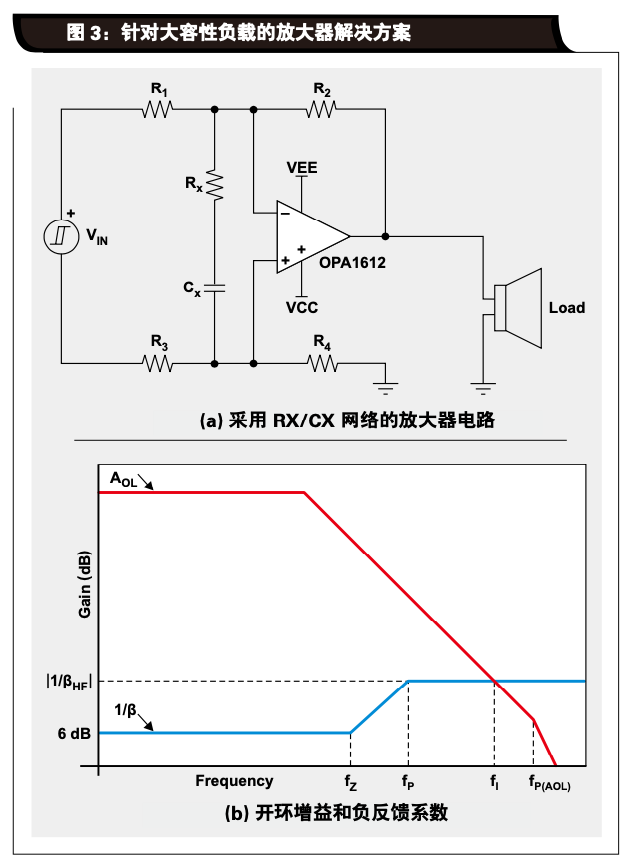

参考 Ti 的 HiFi Audio Circuit Design 以及 实现面向头戴式耳机应用的差动放大器的稳定 :

我使用了如下输出电路,并且使用 TINA 进行仿真:

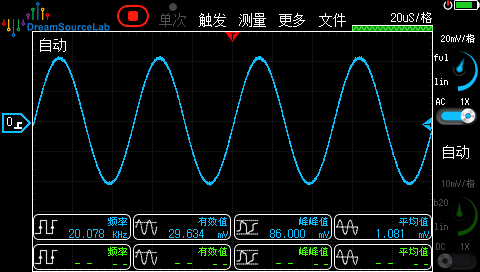

最终成品的 20kHz 输出为(按顺序为 B360i 板载、iPad Air、Desk Cube):

结合 1kHz 的振幅,三者在 20kHz 下的衰减为:-6.3dB,-5.6dB,-13.5dB(DeskCube 在 18kHz 为 -0.2dB,19kHz 为 -5.5dB)。

实际 PCB 设计中需要注意:

- 模拟电路中需选用高精度低温飘电阻(我用的是 0.1% 10ppm 0603 薄膜电阻),C0G/NP0 等级的 MLCC 电容或薄膜电容(如 WIMA )。

- 运放需低噪电源供电,DCDC 电源需远离模拟信号并做好滤波。注意运放工作模式是否为轨至轨,运放发热较高需良好散热。

Summary

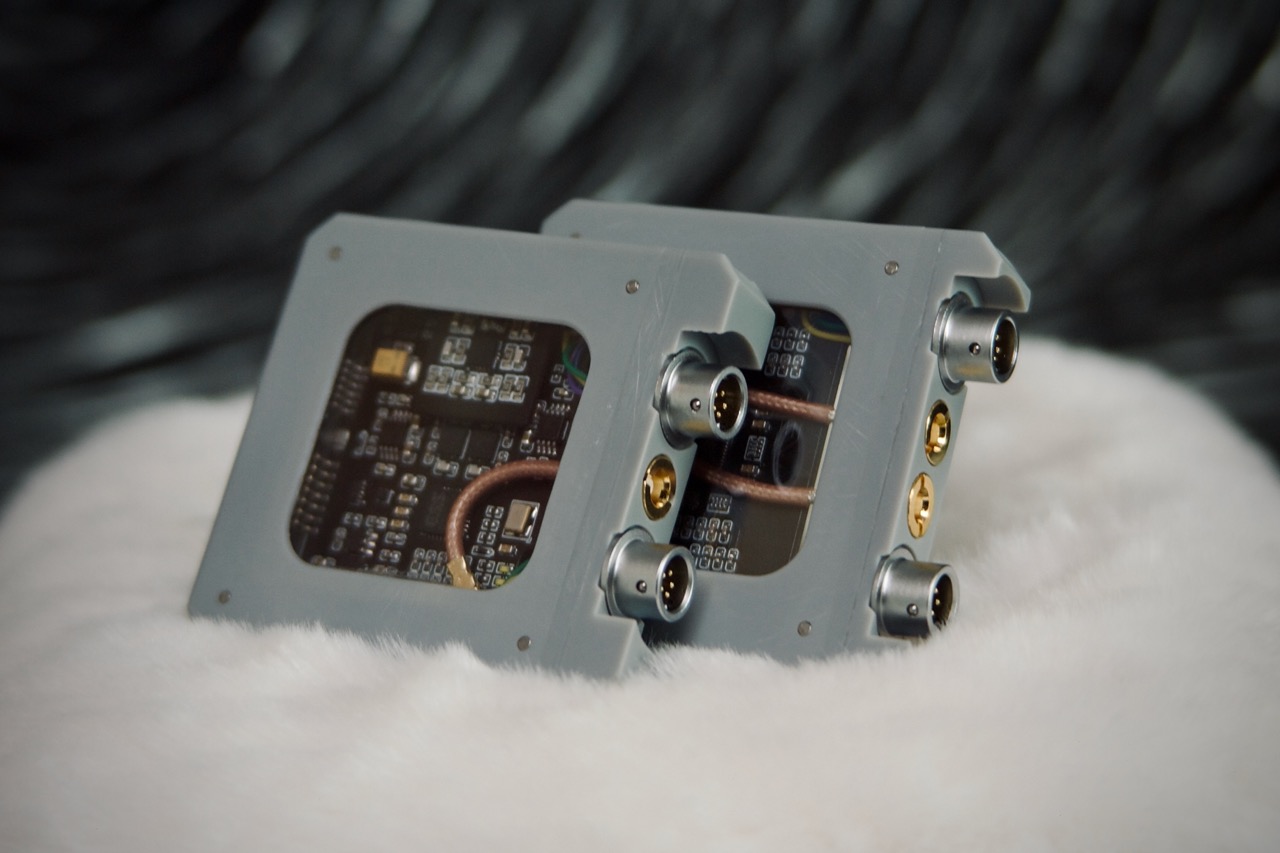

本项目运用了学习到的模电、数电、信号与系统、数字信号处理等知识,多次打样试错总结经验,为此章节画上了个不错的句号。并且为以后可能的模块化预设、尝试了一些标准,未来希望拓展出基于之前的 ADC 制作更高采样率的示波器和逻辑分析、基于 MSI2500 方案的 SDR、USB3 Hub 等模块,实现 IO 以及工具的集中和模块化。

将 I/V 转换后设计为可替换模块,即可根据不同需求替换滤波器或者其他功能。根据 Ti 的 Filter Design 工具设计了 MFB 滤波、使用贴片薄膜电容的 HPF 以及更高输出电压的 TPA6120A2 功放。最后是成品照片以及设计资料:Schematic 、PCB